# BTS5235-2L

Smart High-Side Power Switch

**Automotive Power**

#### **Table of Contents**

# **Table of Contents**

| 1                                                   | Overview                                                                                                                                                                     | . 3                        |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| <b>2</b><br>2.1                                     | Block Diagram                                                                                                                                                                |                            |

| <b>3</b><br>3.1<br>3.2                              | Pin Configuration         Pin Assignment BTS5235-2L         Pin Definitions and Functions                                                                                    | . 7                        |

| <b>4</b><br>4.1                                     | Electrical Characteristics                                                                                                                                                   |                            |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2 | Block Description and Electrical Characteristics  Power Stages Output On-State Resistance Input Circuit Inductive Output Clamp Electrical Characteristics Thermal Resistance | 10<br>10<br>10<br>11<br>13 |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                | Protection Functions Over Load Protection Reverse Polarity Protection Over Voltage Protection Loss of Ground Protection Electrical Characteristics                           | 15<br>16<br>16<br>16       |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4                | Diagnosis ON-State Diagnosis OFF-State Diagnosis Sense Enable Function Electrical Characteristics                                                                            | 19<br>20<br>21             |

| 8                                                   | Package Outlines BTS5235-2L                                                                                                                                                  | 23                         |

| 9                                                   | Revision History                                                                                                                                                             | 24                         |

# Smart High-Side Power Switch PROFET Two Channels, 60 m $\Omega$

BTS5235-2L

#### 1 Overview

#### **Basic Features**

- · Very low standby current

- 3.3 V and 5 V compatible logic pins

- Improved electromagnetic compatibility (EMC)

- · Stable behavior at under voltage

- Logic ground independent from load ground

- · Secure load turn-off while logic ground disconnected

- Optimized inverse current capability

- Green Product (RoHS compliant)

- AEC Qualified

PG-DSO-12-9

#### **Product Summary**

The BTS5235-2L is a dual channel high-side power switch in PG-DSO-12-9 package providing embedded protective functions.

The power transistor is built by a N-channel vertical power MOSFET with charge pump. The device is monolithically integrated in Smart SIPMOS technology.

| Operating voltage                          | $V_{ m bb(on)}$ | 4.5 28 V |

|--------------------------------------------|-----------------|----------|

| Over voltage protection                    | $V_{ m bb(AZ)}$ | 41 V     |

| On-State resistance                        | $R_{DS(ON)}$    | 60 mΩ    |

| Nominal load current (one channel active)  | $I_{L(nom)}$    | 3.5 A    |

| Current limitation                         | $I_{L(LIM)}$    | 23 A     |

| Current limitation repetitive              | $I_{L(SCr)}$    | 6 A      |

| Standby current for whole device with load | $I_{bb(OFF)}$   | 2.5 μΑ   |

| Туре       | Package     | Marking    |

|------------|-------------|------------|

| BTS5235-2L | PG-DSO-12-9 | BTS5235-2L |

Data Sheet 3 Rev.1.0, 2007-06-29

# Smart High-Side Power Switch BTS5235-2L

Overview

#### **Protective Functions**

- · Reverse battery protection without external components

- · Short circuit protection

- Overload protection

- Multi-step current limitation

- Thermal shutdown with restart

- Thermal restart at reduced current limitation

- · Over voltage protection without external resistor

- · Loss of ground protection

- Electrostatic discharge protection (ESD)

#### **Diagnostic Functions**

- Enhanced IntelliSense signal for each channel

- Enable function for diagnosis pins (IS1 and IS2)

- Proportional load current sense signal by current source

- High accuracy of current sense signal at wide load current range

- · Open load detection in ON-state by load current sense

- · Over load (current limitation) diagnosis in ON-state, signalling by voltage source

- Latched over temperature diagnosis in ON-state, signalling by voltage source

- · Open load detection in OFF-state, signalling by voltage source

#### **Applications**

- μC compatible high-side power switch with diagnostic feedback for 12 V grounded loads

- All types of resistive, inductive and capacitive loads

- Suitable for loads with high inrush currents, so as lamps

- Suitable for loads with low currents, so as LEDs

- · Replaces electromechanical relays, fuses and discrete circuits

Data Sheet 4 Rev.1.0, 2007-06-29

**Block Diagram**

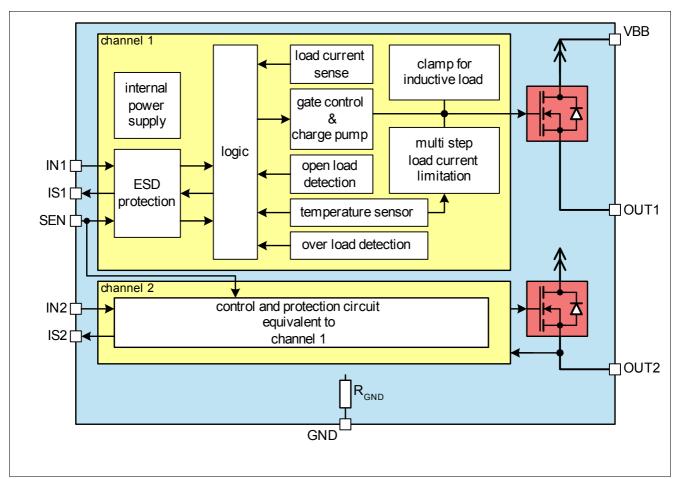

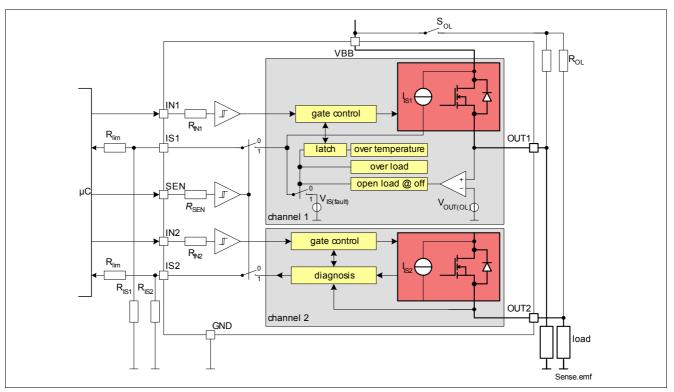

#### 2 Block Diagram

The BTS5235-2L is a dual channel high-side power switch (two times 60 m $\Omega$ ) in PG-DSO-12-9 power package providing embedded protective functions.

The Enhanced IntelliSense pins IS1 and IS2 provide a sophisticated diagnostic feedback signal including current sense function, over load and over temperature alerts in ON-state and open load alert in OFF-state. The diagnosis signals can be switched on and off by the sense enable pin SEN.

An integrated ground resistor as well as integrated resistors at each input pin (IN1, IN2, SEN) reduce external components to a minimum.

The power transistor is built by a N-channel vertical power MOSFET with charge pump.

The inputs are ground referenced CMOS compatible. The device is monolithically integrated in Smart SIPMOS technology.

Figure 1 Block Diagram

Data Sheet 5 Rev.1.0, 2007-06-29

**Block Diagram**

#### 2.1 Terms

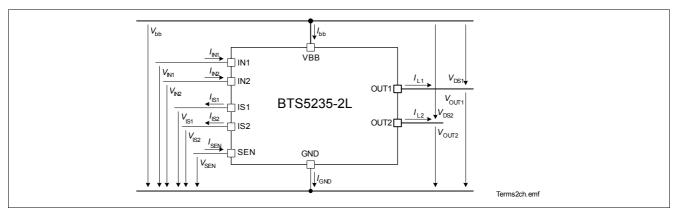

Following figure shows all terms used in this data sheet.

Figure 2 Terms

In all tables of electrical characteristics is valid: Channel related symbols without channel number are valid for each channel separately.

Data Sheet 6 Rev.1.0, 2007-06-29

**Pin Configuration**

# 3 Pin Configuration

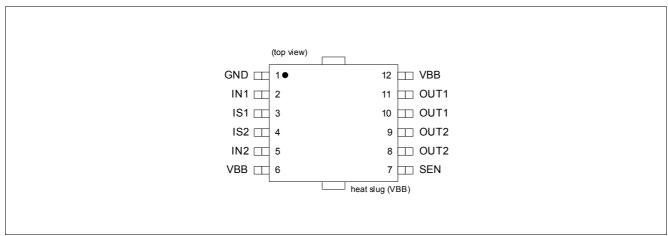

#### 3.1 Pin Assignment BTS5235-2L

Figure 3 Pin Configuration PG-DSO-12-9

#### 3.2 Pin Definitions and Functions

| Pin                | Symbol            | I/O | Function                                                              |

|--------------------|-------------------|-----|-----------------------------------------------------------------------|

| 2                  | IN1               | 1   | Input signal for channel 1                                            |

| 5                  | IN2               | 1   | Input signal for channel 2                                            |

| 3                  | IS1               | 0   | Diagnosis output signal channel 1                                     |

| 4                  | IS2               | 0   | Diagnosis output signal channel 2                                     |

| 7                  | SEN               | I   | Sense Enable input for channel 1&2                                    |

| 10,11              | OUT1 1)           | 0   | Protected high-side power output channel 1                            |

| 8, 9               | OUT2 1)           | 0   | Protected high-side power output channel 2                            |

| 1                  | GND               | _   | Ground connection                                                     |

| 6,12,<br>heat slug | VBB <sup>2)</sup> | -   | Positive power supply for logic supply as well as output power supply |

<sup>1)</sup> All output pins of each channel have to be connected

<sup>2)</sup> All VBB pins have to be connected

**Electrical Characteristics**

# 4 Electrical Characteristics

# 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings 1)

$T_j$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                                                                                   | Symbol             | Limit        | Values       | Unit | Conditions                                                                            |

|--------|-----------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--------------|------|---------------------------------------------------------------------------------------|

|        |                                                                                                                             |                    | min.         | max.         |      |                                                                                       |

| Supply | y Voltage                                                                                                                   | 1                  |              | 1            |      | 1                                                                                     |

| 4.1.1  | Supply voltage                                                                                                              | $V_{bb}$           | -16          | 28           | V    |                                                                                       |

| 4.1.2  | Supply voltage for full short circuit protection (single pulse) $(T_{j(0)} = -40  ^{\circ}\text{C}  150  ^{\circ}\text{C})$ | $V_{\rm bb(SC)}$   | 0            | 28           | V    | $L = 8 \mu H,$<br>$R = 0.2 \Omega^{2}$                                                |

| 4.1.3  | Voltage at power transistor                                                                                                 | $V_{DS}$           | _            | 52           | V    |                                                                                       |

| 4.1.4  | Supply Voltage for Load Dump protection                                                                                     | $V_{ m bb(LD)}$    | -            | 41           | V    | $R_{\rm I} = 2 \Omega^{3)}$<br>$R_{\rm L} = 6.8 \Omega$                               |

| Power  | Stages                                                                                                                      | <u> </u>           |              |              | •    |                                                                                       |

| 4.1.5  | Load current                                                                                                                | $I_{L}$            | -            | $I_{L(LIM)}$ | Α    | 4)                                                                                    |

| 4.1.6  | Maximum energy dissipation single pulse                                                                                     | E <sub>AS</sub>    | -            | 110          | mJ   | $I_{L}(0) = 2 \text{ A}^{5)}$<br>$T_{j}(0) = 150 \text{ °C}$<br>$V_{bb}=13,5\text{V}$ |

| 4.1.7  | Power dissipation (DC)                                                                                                      | $P_{tot}$          | -            | 1.6          | W    | $T_{\rm a}$ = 85 °C <sup>6)</sup> $T_{\rm j} \le$ 150 °C                              |

| Logic  | Pins                                                                                                                        | <u> </u>           |              |              | •    |                                                                                       |

| 4.1.8  | Voltage at input pin                                                                                                        | $V_{IN}$           | -5<br>-16    | 10           | V    | <i>t</i> ≤ 2 min.                                                                     |

| 4.1.9  | Current through input pin                                                                                                   | $I_{IN}$           | -2.0<br>-8.0 | 2.0          | mA   | <i>t</i> ≤ 2 min.                                                                     |

| 4.1.10 | Voltage at sense enable pin                                                                                                 | $V_{SEN}$          | -5<br>-16    | 10           | V    | <i>t</i> ≤ 2 min.                                                                     |

| 4.1.11 | Current through sense enable pin                                                                                            | $I_{SEN}$          | -2.0<br>-8.0 | 2.0          | mA   | <i>t</i> ≤ 2 min.                                                                     |

| 4.1.12 | Current through sense pin                                                                                                   | $I_{IS}$           | -25          | 10           | mA   |                                                                                       |

| Tempe  | eratures                                                                                                                    | 1                  |              | 1            |      |                                                                                       |

| 4.1.13 | Junction Temperature                                                                                                        | $T_{\rm j}$        | -40          | 150          | °C   |                                                                                       |

| 4.1.14 | Dynamic temperature increase while switching                                                                                | $\Delta T_{\rm j}$ | _            | 60           | °C   |                                                                                       |

| 4.1.15 | Storage Temperature                                                                                                         | $T_{stg}$          | -55          | 150          | °C   |                                                                                       |

| ESD S  | usceptibility                                                                                                               |                    |              | 1            | 1    | ı                                                                                     |

| 4.1.16 | ESD susceptibility HBM IN, SEN                                                                                              |                    | -1<br>-2     | 1 2          | kV   | according to<br>EIA/JESD 22-A<br>114B                                                 |

|        | OUT                                                                                                                         |                    | -4           | 4            |      | 1170                                                                                  |

<sup>1)</sup> Not subject to production test, specified by design.

#### Smart High-Side Power Switch BTS5235-2L

#### **Electrical Characteristics**

- 2) R and L describe the complete circuit impedance including line, contact and generator impedances

- 3) Load Dump is specified in ISO 7636,  $R_1$  is the internal resistance of the Load Dump pulse generator

- 4) Current limitation is a protection feature. Operation in current limitation is considered as "outside" normal operating range. Protection features are not designed for continuous repetitive operation.

- 5) Pulse shape represents inductive switch off:  $I_L(t) = I_L(0) * (1 t / t_{pulse}); 0 < t < t_{pulse}$

- 6) Device mounted on PCB (50 mm  $\times$  50 mm  $\times$  1.5mm epoxy, FR4) with 6 cm<sup>2</sup> copper heatsinking area (one layer, 70  $\mu$ m thick) for  $V_{\rm bb}$  connection. PCB is vertical without blown air.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Data Sheet 9 Rev.1.0, 2007-06-29

### 5 Block Description and Electrical Characteristics

#### 5.1 Power Stages

The power stages are built by N-channel vertical power MOSFETs (DMOS) with charge pumps.

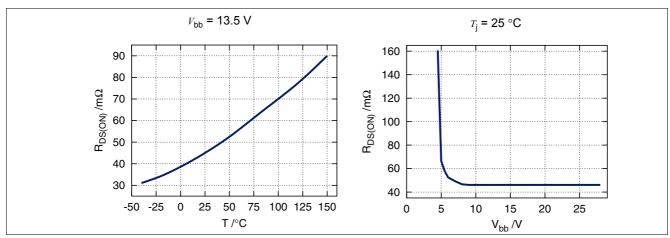

#### 5.1.1 Output On-State Resistance

The on-state resistance  $R_{\rm DS(ON)}$  depends on the supply voltage as well as the junction temperature  $T_{\rm j}$ . Figure 4 shows that dependencies for the typical on-state resistance. The behavior in reverse polarity mode is described in Section 6.2.

Figure 4 Typical On-State Resistance

#### 5.1.2 Input Circuit

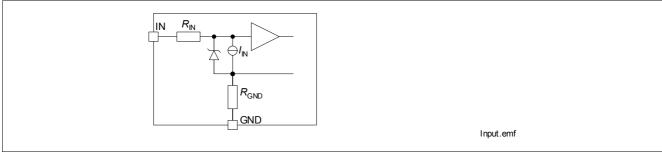

**Figure 5** shows the input circuit of the BTS5235-2L. There is an integrated input resistor that makes external components obsolete. The current sink to ground ensures that the device switches off in case of open input pin. The zener diode protects the input circuit against ESD pulses.

Figure 5 Input Circuit (IN1 and IN2)

Data Sheet 10 Rev.1.0, 2007-06-29

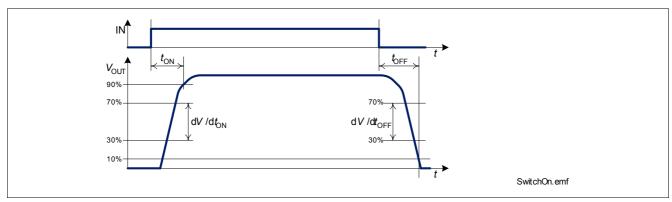

A high signal at the input pin causes the power DMOS to switch on with a dedicated slope, which is optimized in terms of EMC emission.

Figure 6 Switching a Load (resistive)

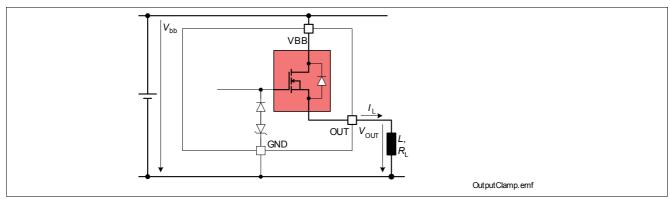

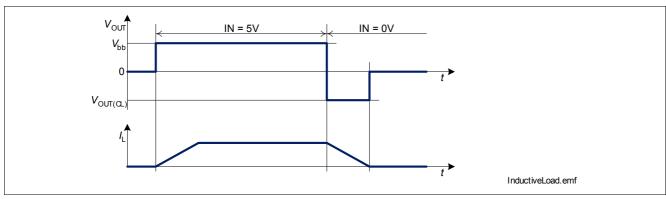

#### 5.1.3 Inductive Output Clamp

When switching off inductive loads with high-side switches, the voltage  $V_{\text{OUT}}$  drops below ground potential, because the inductance intends to continue driving the current.

Figure 7 Output Clamp (OUT1 and OUT2)

To prevent destruction of the device, there is a voltage clamp mechanism implemented that keeps that negative output voltage at a certain level ( $V_{\rm OUT(CL)}$ ). See **Figure 7** and **Figure 8** for details. Nevertheless, the maximum allowed load inductance is limited.

Figure 8 Switching an Inductance

Data Sheet 11 Rev.1.0, 2007-06-29

#### **Maximum Load Inductance**

While demagnetization of inductive loads, energy has to be dissipated in the BTS5235-2L. This energy can be calculated with following equation:

$$E = (V_{bb} - V_{OUT(CL)}) \cdot \left[ \frac{V_{OUT(CL)}}{R_L} \cdot \ln \left( 1 - \frac{R_L \cdot I_L}{V_{OUT(CL)}} \right) + I_L \right] \cdot \frac{L}{R_L}$$

(1)

This equation simplifies under the assumption of  $R_L = 0$ :

$$E = \frac{1}{2}LI_{L}^{2} \cdot \left(1 - \frac{V_{bb}}{V_{OUT(CL)}}\right) \tag{2}$$

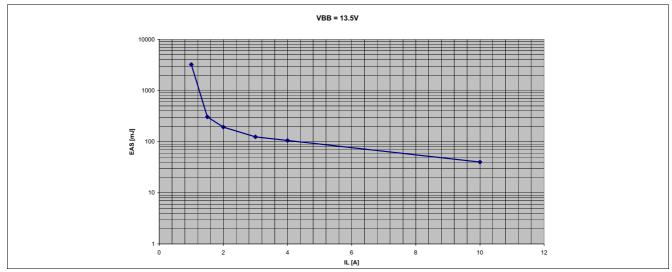

The energy, which is converted into heat, is limited by the thermal design of the component. See **Figure 9** for the maximum allowed energy dissipation.

Figure 9 Maximum Energy Dissipation Single Pulse,  $T_{i,Start}$  = 150 °C

Data Sheet 12 Rev.1.0, 2007-06-29

#### **5.1.4** Electrical Characteristics

Unless otherwise specified:

$V_{\rm bb}$  = 9 V to 16 V,  $T_{\rm j}$  = -40 °C to +150 °C, typical values:  $V_{\rm bb}$  = 13.5 V,  $T_{\rm j}$  = 25 °C

| Pos.   | Parameter                                                               | Symbol                          | Lin         | nit Val       | ues              | Unit | <b>Test Conditions</b>                                                                                                             |

|--------|-------------------------------------------------------------------------|---------------------------------|-------------|---------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                         |                                 | min.        | typ.          | max.             |      |                                                                                                                                    |

| Gene   | ral                                                                     | -                               | +           |               |                  | 1    |                                                                                                                                    |

| 5.1.1  | Operating voltage                                                       | $V_{bb}$                        | 4.5         | _             | 28               | V    | $V_{\rm IN}$ = 4.5 V<br>$R_{\rm L}$ = 12 $\Omega$<br>$V_{\rm DS}$ < 0.5 V                                                          |

| 5.1.2  | Operating current one channel active all channels active                | $I_{GND}$                       | _<br>_      | 1.8<br>3.6    | 4.0<br>8.0       | mA   | V <sub>IN</sub> = 5 V                                                                                                              |

| 5.1.3  | Standby current for whole device with load                              | $I_{\mathrm{bb}(\mathrm{OFF})}$ | -<br>-<br>- | 1.5<br>-<br>- | 2.5<br>2.5<br>15 | μΑ   | $V_{IN} = 0 \text{ V}$<br>$V_{SEN} = 0 \text{ V}$<br>$T_j = 25 \text{ °C}$<br>$T_j = 85 \text{ °C}^{1)}$<br>$T_j = 150 \text{ °C}$ |

| Outpu  | it Characteristics                                                      |                                 |             |               |                  | •    |                                                                                                                                    |

| 5.1.4  | On-State resistance per channel                                         | $R_{DS(ON)}$                    | _<br>_      | 45<br>90      | 60<br>115        | mΩ   | $I_{L}$ = 2.5 A<br>$T_{j}$ = 25 °C<br>$T_{j}$ = 150 °C                                                                             |

| 5.1.5  | Output voltage drop limitation at small load currents                   | $V_{\mathrm{DS(NL)}}$           | _           | 40            | _                | mV   | <i>I</i> <sub>L</sub> < 0.25 A                                                                                                     |

| 5.1.6  | Nominal load current per channel one channel active two channels active | $I_{L(nom)}$                    | 3.5<br>2.6  |               |                  | A    | $T_{\rm a}$ = 85 °C<br>$T_{\rm j} \le$ 150 °C <sup>2) 3)</sup>                                                                     |

|        | ISO load current per channel one channel active two channels active     | $I_{L(ISO)}$                    | 5.3<br>5.3  |               |                  | A    | $T_{\rm c}$ = 85 °C<br>$V_{\rm DS}$ = 0.5 V <sup>3)</sup>                                                                          |

| 5.1.7  | Output clamp                                                            | $V_{OUT(CL)}$                   | -24         | -20           | -17              | V    | I <sub>L</sub> = 40 mA                                                                                                             |

| 5.1.8  | Output leakage current per channel                                      | $I_{L(OFF)}$                    | _           | 0.1           | 6.0              | μА   | $V_{\text{IN}} = 0 \text{ V}$                                                                                                      |

| 5.1.9  | Inverse current capability                                              | -IL(inv)                        | _           | 3             | _                | Α    | 1)                                                                                                                                 |

| Input  | Characteristics                                                         | 1                               | 1           | ı             | 1                | 1    | 1                                                                                                                                  |

| 5.1.10 | Input resistor                                                          | $R_{IN}$                        | 1.8         | 3.5           | 5.5              | kΩ   |                                                                                                                                    |

| 5.1.11 | L-input level                                                           | $V_{IN(L)}$                     | -0.3        | _             | 1.0              | V    |                                                                                                                                    |

| 5.1.12 | H-input level                                                           | $V_{IN(H)}$                     | 2.5         | _             | 5.7              | V    |                                                                                                                                    |

| 5.1.13 | L-input current                                                         | $I_{IN(L)}$                     | 3           | 18            | 75               | μΑ   | V <sub>IN</sub> = 0.4 V                                                                                                            |

| 5.1.14 | H-input current                                                         | $I_{IN(H)}$                     | 10          | 38            | 75               | μΑ   | V <sub>IN</sub> = 5 V                                                                                                              |

| Timin  | gs                                                                      |                                 |             |               |                  |      |                                                                                                                                    |

| 5.1.15 | Turn-on time to 90% $V_{\rm bb}$                                        | $t_{ON}$                        | -           | 100           | 250              | μS   | $R_{\rm L}$ = 12 $\Omega$<br>$V_{\rm bb}$ = 13.5 V                                                                                 |

| 5.1.16 | Turn-off time to 10% $V_{\rm bb}$                                       | $t_{OFF}$                       | _           | 120           | 250              | μS   | $R_{\rm L} = 12 \Omega$<br>$V_{\rm bb} = 13.5 \rm V$                                                                               |

Data Sheet 13 Rev.1.0, 2007-06-29

Unless otherwise specified:

$V_{\rm bb}$  = 9 V to 16 V,  $T_{\rm i}$  = -40 °C to +150 °C, typical values:  $V_{\rm bb}$  = 13.5 V,  $T_{\rm i}$  = 25 °C

| Pos.   | Parameter                         | Symbol               | Lin  | Limit Values |      |      | <b>Test Conditions</b>                                 |

|--------|-----------------------------------|----------------------|------|--------------|------|------|--------------------------------------------------------|

|        |                                   |                      | min. | typ.         | max. |      |                                                        |

| 5.1.17 | slew rate 30% to 70% $V_{\rm bb}$ | ${ m d}V_{ m /dtON}$ | 0.1  | 0.25         | 0.5  | V/µs | $R_{\rm L} = 12 \Omega$<br>$V_{\rm bb} = 13.5 {\rm V}$ |

| 5.1.18 | slew rate 70% to 30% $V_{\rm bb}$ | -d $V_{ m /dtOFF}$   | 0.1  | 0.25         | 0.5  | V/μs | $R_{\rm L} = 12 \Omega$<br>$V_{\rm bb} = 13.5 {\rm V}$ |

<sup>1)</sup> Not subject to production test, specified by design

Note: Characteristics show the deviation of parameter at the given supply voltage and junction temperature.

Typical values show the typical parameters expected from manufacturing.

#### 5.2 Thermal Resistance

| Pos.  | Parameter                      | Symbol     | L    | imit Valu | Unit | Conditions |    |

|-------|--------------------------------|------------|------|-----------|------|------------|----|

|       |                                |            | Min. | Тур.      | Max. |            |    |

| 5.2.1 | Junction to Case <sup>1)</sup> | $R_{thJC}$ | _    | _         | 2.2  | K/W        | _  |

| 5.2.2 | Junction to Ambient            | $R_{thJA}$ |      | _         | _    | K/W        | 2) |

|       | one channel active             |            | _    | 45        | _    |            |    |

|       | all channels active            |            | _    | 40        | _    |            |    |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 14 Rev.1.0, 2007-06-29

<sup>2)</sup> Device mounted on PCB (50 mm  $\times$  50 mm  $\times$  1.5mm epoxy, FR4) with 6 cm<sup>2</sup> copper heatsinking area (one layer, 70  $\mu$ m thick) for  $V_{\rm bb}$  connection. PCB is vertical without blown air.

<sup>3)</sup> Not subject to production test, parameters are calculated from  $R_{

m DS(ON)}$  and  $R_{

m th}$

<sup>2)</sup> Device mounted on PCB (50 mm  $\times$  50 mm  $\times$  1.5mm epoxy, FR4) with 6 cm<sup>2</sup> copper heatsinking area (one layer, 70  $\mu$ m thick) for  $V_{bb}$  connection. PCB is vertical without blown air.

**Protection Functions**

#### 6 Protection Functions

The device provides embedded protective functions. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are neither designed for continuous nor repetitive operation.

#### 6.1 Over Load Protection

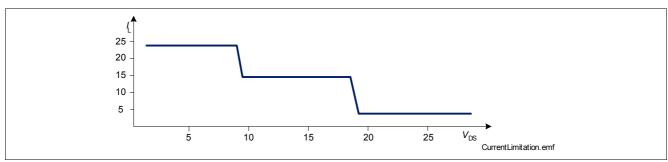

The load current  $I_{\mathsf{OUT}}$  is limited by the device itself in case of over load or short circuit to ground. There are three steps of current limitation which are selected automatically depending on the voltage  $V_{\mathsf{DS}}$  across the power DMOS. Please note that the voltage at the OUT pin is  $V_{\mathsf{bb}}$  -  $V_{\mathsf{DS}}$ . Please refer to following figure for details.

Figure 10 Current Limitation (minimum values)

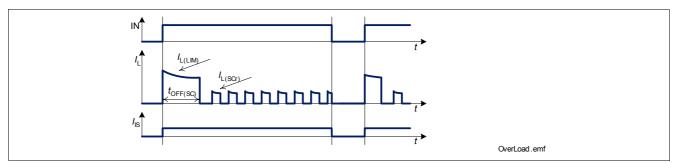

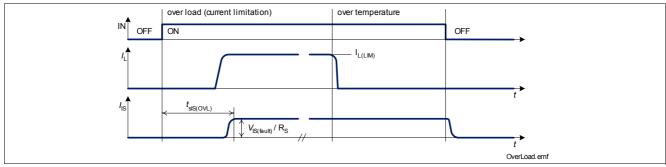

Current limitation is realized by increasing the resistance of the device which leads to rapid temperature rise inside. A temperature sensor for each channel causes an overheated channel to switch off to prevent destruction. After cooling down with thermal hysteresis, the channel switches on again. Please refer to **Figure 11** for details.

Figure 11 Shut Down by Over Temperature with Current Limitation

In short circuit condition, the load current is initially limited to  $I_{L(LIM)}$ . After thermal restart, the current limitation level is reduced to  $I_{L(SCr)}$ . The current limitation level is reset to  $I_{L(LIM)}$  by switching off the device ( $V_{IN} = 0 \text{ V}$ ).

Data Sheet 15 Rev.1.0, 2007-06-29

**Protection Functions**

#### 6.2 Reverse Polarity Protection

In case of reverse polarity, the intrinsic body diode causes power dissipation. Additional power is dissipated by the integrated ground resistor. Use following formula for estimation of total power dissipation  $P_{\sf diss(rev)}$  in reverse polarity mode.

$$P_{\text{diss(rev)}} = \sum_{\text{all channels}} (V_{\text{DS(rev)}} \cdot I_{\text{L}}) + \frac{V_{\text{bb}}^2}{R_{\text{GND}}}$$

(3)

The reverse current through the intrinsic body diode has to be limited by the connected load. The current through sense pins IS1 and IS2 has to be limited (please refer to maximum ratings on **Page 8**). The current through the ground pin (GND) is limited internally by  $R_{\text{GND}}$ . The over-temperature protection is not active during reverse polarity.

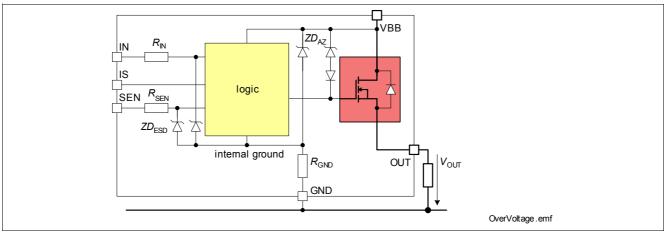

#### 6.3 Over Voltage Protection

In addition to the output clamp for inductive loads as described in **Section 5.1.3**, there is a clamp mechanism for over voltage protection. Because of the integrated ground resistor, over voltage protection does not require external components.

As shown in **Figure 12**, in case of supply voltages greater than  $V_{bb(AZ)}$ , the power transistor switches on and the voltage across logic part is clamped. As a result, the internal ground potential rises to  $V_{bb}$  -  $V_{bb(AZ)}$ . Due to the ESD zener diodes, the potential at pin IN1, IN2 and SEN rises almost to that potential, depending on the impedance of the connected circuitry.

Figure 12 Over Voltage Protection

#### 6.4 Loss of Ground Protection

In case of complete loss of the device ground connections, but connected load ground, the BTS5235-2L securely changes to or stays in off state.

Data Sheet 16 Rev.1.0, 2007-06-29

**Protection Functions**

### 6.5 Electrical Characteristics

Unless otherwise specified:

$V_{\rm bb}$  = 9 V to 16 V,  $T_{\rm j}$  = -40 °C to +150 °C, typical values:  $V_{\rm bb}$  = 13.5 V,  $T_{\rm j}$  = 25 °C

| Pos.   | Parameter                                         | Symbol                   | Lin  | nit Val   | ues  | Unit | Conditions                                     |

|--------|---------------------------------------------------|--------------------------|------|-----------|------|------|------------------------------------------------|

|        |                                                   |                          | min. | typ.      | max. |      |                                                |

| Over   | Load Protection                                   | ·                        | -    | •         |      | •    | -1                                             |

| 6.5.1  | Load current limitation                           | $I_{L(LIM)}$             | 23   | _         | 42   | Α    | V <sub>DS</sub> = 7 V                          |

|        |                                                   |                          | 14   | _         | 28   | Α    | $V_{\rm DS}$ = 14 V                            |

|        |                                                   |                          | 3    | _         | 14   | Α    | $V_{\rm DS}$ = 28 V <sup>1) 2)</sup>           |

| 6.5.2  | Repetitive short circuit current limitation       | $I_{L(SCr)}$             | _    | 6         | _    | Α    | $T_{\rm j} = T_{\rm j(SC)}^{2)}$               |

| 6.5.3  | Initial short circuit shut down time              | $t_{OFF(SC)}$            |      | 8.0       |      | ms   | $T_{\rm jStart}$ = 25 °C <sup>2)</sup>         |

| 6.5.4  | Thermal shut down temperature                     | $T_{ m j(SC)}$           | 150  | 170<br>2) | _    | °C   |                                                |

| 6.5.5  | Thermal hysteresis                                | $\Delta T_{ m j}$        | -    | 7         | _    | K    | 2)                                             |

| Revei  | se Battery                                        |                          |      |           |      |      |                                                |

| 6.5.6  | Drain-Source diode voltage ( $V_{OUT} > V_{bb}$ ) | - $V_{\mathrm{DS(rev)}}$ | _    | _         | 900  | mV   | $I_{\rm L}$ = -3.5 A                           |

|        |                                                   |                          |      |           |      |      | $V_{\rm bb} = -13.5 \text{ V}$                 |

|        |                                                   |                          |      |           |      |      | <i>T</i> <sub>j</sub> = 150 °C                 |

| 6.5.7  | Reverse current through GND pin                   | -IGND                    | _    | 65        | _    | mA   | $V_{\rm bb}$ = -13.5 V <sup>2)</sup>           |

| Groui  | nd Circuit                                        |                          |      |           |      |      |                                                |

| 6.5.8  | Integrated Resistor in GND line                   | $R_{GND}$                | 115  | 220       | 350  | Ω    |                                                |

| Over   | Voltage                                           |                          |      |           | •    |      |                                                |

| 6.5.9  | Over voltage protection                           | $V_{\mathrm{bb(AZ)}}$    | 41   | 47        | 53   | V    | $I_{\rm bb}$ = 2 mA                            |

| Loss   | of GND                                            | <u>'</u>                 | •    |           | •    |      | •                                              |

| 6.5.10 | Output leakage current while GND                  | $I_{L(GND)}$             | _    | _         | 1    | mA   | $I_{\rm IN} = 0, I_{\rm SEN} = 0, I_{\rm SEN}$ |

|        | disconnected                                      |                          |      |           |      |      | = 0,                                           |

|        |                                                   |                          |      |           |      |      | $I_{\text{GND}} = 0^{2)3}$                     |

<sup>1)</sup> Please note that an external forced  $V_{\rm DS}$  must not exceed  $V_{\rm bb}$  +  $|V_{\rm OUT(CL)}|$

Data Sheet 17 Rev.1.0, 2007-06-29

<sup>2)</sup> Not subject to production test, specified by design

<sup>3)</sup> Pins not connected

# 7 Diagnosis

For diagnosis purpose, the BTS5235-2L provides an Enhanced IntelliSense signal at pins IS1 and IS2. This means in detail, the current sense signal  $I_{\rm IS}$ , a proportional signal to the load current (ratio  $k_{\rm ILIS} = I_{\rm L} / I_{\rm IS}$ ), is provided as long as no failure mode (see **Table 1**) occurs. In case of a failure mode, the voltage  $V_{\rm IS(fault)}$  is fed to the diagnosis pin.

Figure 13 Block Diagram: Diagnosis

Table 1 Truth Table 1)

| Operation Mode                | Input       | Output                 | Diagnostic Output                       |         |  |  |  |

|-------------------------------|-------------|------------------------|-----------------------------------------|---------|--|--|--|

|                               | Level Level |                        | SEN = H                                 | SEN = L |  |  |  |

| Normal Operation (OFF)        | L           | GND                    | Z                                       | Z       |  |  |  |

| Short Circuit to GND          |             | GND                    | Z                                       | Z       |  |  |  |

| Over Temperature              |             | Z                      | Z                                       | Z       |  |  |  |

| Short Circuit to $V_{\rm bb}$ |             | $V_{bb}$               | $V_{\rm IS} = V_{\rm IS(fault)}$        | Z       |  |  |  |

| Open Load                     |             | < V <sub>OUT(OL)</sub> | Z                                       | Z       |  |  |  |

|                               |             | $> V_{\rm OUT(OL)}$    | $V_{\rm IS}$ = $V_{\rm IS(fault)}$      | Z       |  |  |  |

| Normal Operation (ON)         | Н           | $\sim V_{ m bb}$       | $I_{\rm IS} = I_{\rm L} / k_{\rm ILIS}$ | Z       |  |  |  |

| Current Limitation            |             | < V <sub>bb</sub>      | $V_{\rm IS} = V_{\rm IS(fault)}$        | Z       |  |  |  |

| Short Circuit to GND          |             | ~GND                   | $V_{\rm IS} = V_{\rm IS(fault)}$        | Z       |  |  |  |

| Over Temperature              |             | Z                      | $V_{\rm IS} = V_{\rm IS(fault)}$        | Z       |  |  |  |

| Short Circuit to $V_{\rm bb}$ |             | $V_{bb}$               | $I_{\rm IS} < I_{\rm L} / k_{\rm ILIS}$ | Z       |  |  |  |

| Open Load                     |             | $V_{bb}$               | Z                                       | Z       |  |  |  |

<sup>1)</sup> L = Low Level, H = High Level, Z = high impedance, potential depends on leakage currents and external circuit

Data Sheet 18 Rev.1.0, 2007-06-29

#### 7.1 ON-State Diagnosis

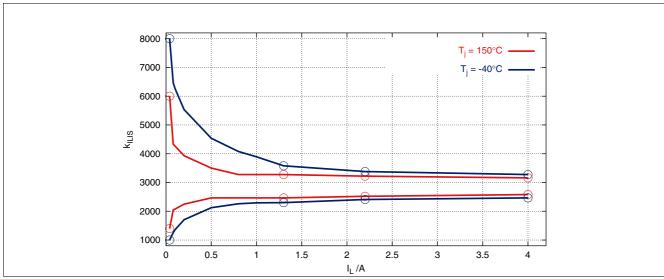

The standard diagnosis signal is a current sense signal proportional to the load current. The accuracy of the ratio  $(k_{\rm ILIS} = I_{\rm L} / I_{\rm IS})$  depends on the temperature. Please refer to following **Figure 14** for details. Usually a resistor  $R_{\rm IS}$  is connected to the current sense pin. It is recommended to use sense resistors  $R_{\rm IS} > 500~\Omega$ . A typical value is 4.7 k $\Omega$ .

Figure 14 Current sense ratio  $k_{\rm ILIS}^{1}$

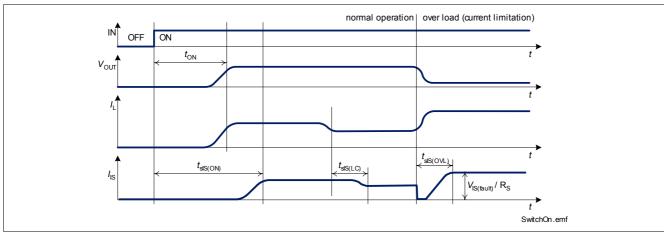

Details about timings between the diagnosis signal  $I_{\rm IS}$  and the output voltage  $V_{\rm OUT}$  and load current  $I_{\rm L}$  in ON-state can be found in Figure 15.

Figure 15 Timing of Diagnosis Signal in ON-state

In case of over-load as well as over-temperature, the voltage  $V_{\rm IS(fault)}$  is fed to the diagnosis pins as long as the according input pin is high. This means, even if the overload disappears after the first thermal shutdown or when the device keeps switching on and off in over-load condition (thermal toggling), the diagnosis signal ( $V_{\rm IS(fault)}$ ) is constantly available. Please refer to **Figure 16** for details. Please note, that if the overload disappears before the first thermal shutdown, the diagnosis signal ( $V_{\rm IS(fault)}$ ) may remain for approximately 300  $\mu$ s longer than the duration of the overload.

Data Sheet 19 Rev.1.0, 2007-06-29

<sup>1)</sup> The curves show the behavior based on characterization data. The marked points are guaranteed in this Data Sheet in Section 7.4 (Position 7.4.6).

As a result open load and over load including over temperature can be differentiated in ON-state.

Consideration must be taken in the selection of the sense resistor in order to distinguish nominal currents from the overload/short circuit fault state. A potential of 5 V at the sense pin can be achieved with a big sense resistor even with currents being much smaller than the current limitation.

Figure 16 Timing of Diagnosis Signal in Over Load Condition

#### 7.2 OFF-State Diagnosis

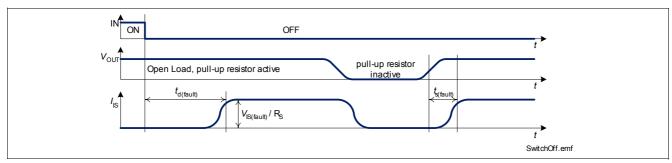

Details about timings between the diagnosis signal  $I_{\rm IS}$  and the output voltage  $V_{\rm OUT}$  and load current  $I_{\rm L}$  in OFF-state can be found in **Figure 17**. For open load diagnosis in OFF-state an external output pull-up resistor ( $R_{\rm OL}$ ) is necessary.

Figure 17 Timing of Diagnosis Signal in OFF-state

For calculation of the pull-up resistor, just the external leakage current  $I_{\text{leakage}}$  and the open load threshold voltage  $V_{\text{OUT(OL)}}$  has to be taken into account.

$$R_{\rm OL} = \frac{V_{\rm bb(min)} - V_{\rm OUT(OL,max)}}{I_{\rm leakage}}$$

(4)

$I_{\rm leakage}$  defines the leakage current in the complete system e.g. caused by humidity. There is no internal leakage current from out to ground at BTS5235-2L.  $V_{\rm bb(min)}$  is the minimum supply voltage at which the open load diagnosis in off state must be ensured. To reduce the stand-by current of the system, an open load resistor switch ( $S_{\rm OL}$ ) is recommended.

Data Sheet 20 Rev.1.0, 2007-06-29

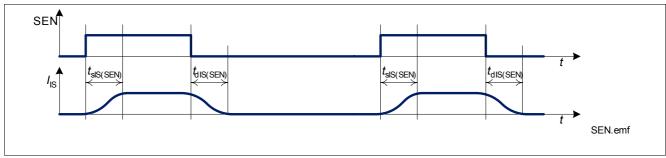

#### 7.3 Sense Enable Function

The diagnosis signals have to be switched on by a high signal at sense enable pin (SEN). See **Figure 18** for details on the timing between SEN pin and diagnosis signal  $I_{\rm IS}$ . Please note that the diagnosis is disabled, when no signal is provided at pin SEN.

Figure 18 Timing of Sense Enable Signal

The SEN pin circuit is designed equally to the input pin. Please refer to **Figure 5** for details. The resistors  $R_{lim}$  are recommended to limit the current through the sense pins IS1 and IS2 in case of reverse polarity and over voltage. Please refer to maximum ratings on **Page 8**.

The stand-by current of the BTS5235-2L is minimized, when both input pins (IN1 and IN2) and the sense enable pin (SEN) are on low level.

#### 7.4 Electrical Characteristics

$V_{\rm bb}$  = 9 V to 16 V,  $T_{\rm j}$  = -40 °C to +150 °C,  $V_{\rm SEN}$  = 5 V, (unless otherwise specified) typical values:  $V_{\rm bb}$  = 13.5 V,  $T_{\rm j}$  = 25 °C

| Pos.  | Parameter                                             | Symbol                | Limit Values |      |      | Unit | Conditions                                                                                             |

|-------|-------------------------------------------------------|-----------------------|--------------|------|------|------|--------------------------------------------------------------------------------------------------------|

|       |                                                       |                       | min.         | typ. | max. |      |                                                                                                        |

| Gene  | ral Definition                                        | 1                     | 1            |      | 1    | •    | -1                                                                                                     |

| 7.4.1 | Diagnostics signal in failure mode                    | $V_{IS(fault)}$       | 5            | _    | 9    | V    | $V_{\rm IN}$ = 0 V<br>$V_{\rm OUT}$ = $V_{\rm bb}$<br>$I_{\rm IS}$ = 1 mA                              |

| 7.4.2 | Diagnostics signal current limitation in failure mode | $I_{IS(LIM)}$         | 3            | _    | _    | mA   | $V_{\text{IN}} = 0 \text{ V}$ $V_{\text{OUT}} = V_{\text{bb}}$                                         |

| Open  | Load at OFF-State                                     |                       |              |      |      |      |                                                                                                        |

| 7.4.3 | Open load detection threshold voltage                 | $V_{OUT(OL)}$         | 1.6          | 2.8  | 4.4  | V    |                                                                                                        |

| 7.4.4 | Sense signal invalid after negative input slope       | t <sub>d(fault)</sub> | _            | _    | 1.2  | ms   | $V_{\text{IN}}$ = 5 V to 0 V<br>$V_{\text{OUT}}$ = $V_{\text{bb}}$                                     |

| 7.4.5 | Fault signal settling time                            | t <sub>s(fault)</sub> | _            | _    | 200  | μS   | $V_{\text{IN}}$ = 0 V<br>$V_{\text{OUT}}$ = 0 V to<br>> $V_{\text{OUT(OL)}}$<br>$I_{\text{IS}}$ = 1 mA |

Data Sheet 21 Rev.1.0, 2007-06-29

$V_{\rm bb}$  = 9 V to 16 V,  $T_{\rm j}$  = -40 °C to +150 °C,  $V_{\rm SEN}$  = 5 V, (unless otherwise specified) typical values:  $V_{\rm bb}$  = 13.5 V,  $T_{\rm j}$  = 25 °C

| Pos.   | Parameter                                                                                  | Symbol             | Lin          | nit Val      | ues                   | Unit | Conditions                                                          |

|--------|--------------------------------------------------------------------------------------------|--------------------|--------------|--------------|-----------------------|------|---------------------------------------------------------------------|

|        |                                                                                            |                    | min.         | typ.         | max.                  | 1    |                                                                     |

| Load   | Current Sense ON-State                                                                     |                    |              |              |                       |      |                                                                     |

| 7.4.6  | Current sense ratio                                                                        | $k_{ILIS}$         | _            | 2870         | _                     |      | V <sub>IN</sub> = 5 V                                               |

|        | $I_{L}$ = 40 mA                                                                            |                    | 1000         | 4035         | 8000                  |      | <i>T</i> <sub>i</sub> = -40 °C                                      |

|        | $I_{L}$ = 1.3 A                                                                            |                    | 2300         | 3050         |                       |      |                                                                     |

|        | $I_{L} = 2.2 \text{ A}$                                                                    |                    | 2410         | 2920         |                       |      |                                                                     |

|        | $I_{\rm L}$ = 4.0 A                                                                        |                    | 2465         | 2850         |                       |      |                                                                     |

|        | $I_{L} = 40 \text{ mA}$                                                                    |                    | 1400         | 3410         |                       |      | $T_{\rm j}$ = 150 °C                                                |

|        | $I_{L} = 1.3 \text{ A}$                                                                    |                    | 2465         | 2920         | 3275                  |      |                                                                     |

|        | $I_{L} = 2.2 \text{ A}$<br>$I_{L} = 4.0 \text{ A}$                                         |                    | 2520<br>2580 | 2875<br>2870 |                       |      |                                                                     |

| 7.4.7  | Current sense voltage limitation                                                           | V                  | 5.0          | 6.2          | 7.5                   | V    | I <sub>IS</sub> = 0.5 mA                                            |

| 1.4.1  | Current sense voltage innitiation                                                          | $V_{IS(LIM)}$      | 3.0          | 0.2          | 7.5                   | V    | $I_{\rm L} = 3.5  {\rm A}$                                          |

| 7.4.8  | Current sense leakage/offset current                                                       | $I_{IS(LH)}$       | _            | _            | 3.5                   | μΑ   | V <sub>IN</sub> = 5 V                                               |

|        |                                                                                            |                    |              |              |                       |      | $I_{L} = 0 \; A$                                                    |

| 7.4.9  | Current sense leakage, while diagnosis                                                     | $I_{IS(dis)}$      | _            | _            | 1                     | μΑ   | $V_{SEN}$ = 0 V                                                     |

|        | disabled                                                                                   |                    |              |              |                       |      | $I_{\rm L}$ = 3.5 A                                                 |

| 7.4.10 | Current sense settling time to $I_{IS}$ static ±10%                                        | $t_{\sf sIS(ON)}$  | _            | _            | 350                   | μS   | $V_{IN} = 0 \text{ V to 5 V}$                                       |

|        | after positive input slope                                                                 |                    |              |              |                       |      | $I_{\rm L}$ = 3.5 A <sup>1)</sup>                                   |

| 7.4.11 | Current sense settling time to $I_{\rm IS}$ static $\pm 10\%$ after change of load current | $t_{\rm sIS(LC)}$  | _            | _            | 50                    | μS   | $V_{IN} = 5 \text{ V}$<br>$I_{L} = 1.3 \text{ A to } 2.2 \text{ A}$ |

| Over   | Load in ON-State                                                                           |                    |              |              |                       |      |                                                                     |

| 7.4.12 | Over load detection current                                                                | $I_{L(OVL)}$       | 8            | _            | $I_{\mathrm{L(LIM)}}$ | Α    | V <sub>IN</sub> = 5 V                                               |

|        |                                                                                            | , ,                |              |              | , ,                   |      | $V_{\rm IS} = V_{\rm IS(fault)}$                                    |

|        |                                                                                            |                    |              |              |                       |      | 1)                                                                  |

| 7.4.13 | Sense signal settling time in overload condition                                           | $t_{\sf sIS(OVL)}$ | _            | _            | 200                   | μS   | $V_{OUT}$ = 2 V                                                     |

|        |                                                                                            |                    |              |              |                       |      | $V_{\text{IN}}$ = 0 V to 5 V                                        |

|        | Enable                                                                                     |                    | 1            | I            | I                     | 1    |                                                                     |

|        | Input resistance                                                                           | $R_{SEN}$          | 1.8          | 3.5          | 5.5                   | kΩ   |                                                                     |

| 7.4.15 | L-input level                                                                              | $V_{SEN(L)}$       | -0.3         | _            | 1.0                   | V    |                                                                     |

| 7.4.16 | H-input level                                                                              | $V_{\rm SEN(H)}$   | 2.5          | _            | 5.7                   | V    |                                                                     |

| 7.4.17 | L-input current                                                                            | $I_{\rm SEN(L)}$   | 3            | 18           | 75                    | μΑ   | $V_{SEN}$ = 0.4 V                                                   |

| 7.4.18 | H-input current                                                                            | $I_{SEN(H)}$       | 10           | 38           | 75                    | μΑ   | $V_{SEN}$ = 5 V                                                     |

| 7.4.19 | Current sense settling time                                                                | $t_{\rm sIS(SEN)}$ | _            | 3            | 25                    | μS   | $V_{\text{SEN}}$ = 0 V to 5 V                                       |

|        |                                                                                            | , ,                |              |              |                       |      | $V_{\text{IN}} = 0 \text{ V}$                                       |

|        |                                                                                            |                    |              |              |                       |      | $V_{\text{OUT}} > V_{\text{OUT(OL)}}$                               |

| 7.4.20 | Current sense deactivation time                                                            | $t_{\sf dIS(SEN)}$ | _            | _            | 25                    | μS   | $V_{\text{SEN}}$ = 5 V to 0 V                                       |

|        |                                                                                            |                    |              |              |                       |      | $I_{L} = 3.5 \text{ A}$                                             |

|        |                                                                                            |                    |              |              |                       |      | $R_{\rm S}$ = 5 k $\Omega^{1}$                                      |

<sup>1)</sup> Not subject to production test, specified by design

Package Outlines BTS5235-2L

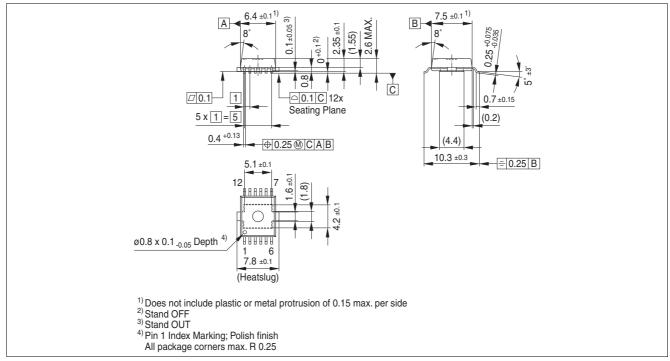

# 8 Package Outlines BTS5235-2L

Figure 19 PG-DSO-12-9 (Plastic Dual Small Outline Package)

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

# 9 Revision History

| Version | Date       | Changes                                                                                                                                                                                      |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev.1.0 | 2007-06-29 | all pages: added new Infineon logo Creation of the green data sheet. First page: Adding the green logo and the AEC qualified Adding the bullet AEC qualified and the RoHS compliant features |

|         |            | Package page Modification of the package to be green.                                                                                                                                        |

|         |            | Data sheet derived from the BTS5235L grey Revision 1.0: parameter 4.1.6: change to 110mJ at 12V; added conditions Vbb=13.5V changed Figure 9. parameter 4.1.7: -24V min17V max.              |

Data Sheet 24 Rev.1.0, 2007-06-29

Edition 2007-06-29

Published by Infineon Technologies AG 81726 Munich, Germany © 7/2/07 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.